本篇文章在已有的基础上,继续给验证平台添加reference model 和scoreboard组件。

https://github.com/shirainbown/UVM-Step-by-Step/tree/master

1. reference model

reference model 用于接收来自monitor的数据,也即DUT 的输入端口的数据,然后模拟DUT 的行为,计算正确的输出结果然后把结果输出给scoreboard。

`ifndef MY_MODEL__SV

`define MY_MODEL__SV

class my_model extends uvm_component;

uvm_blocking_get_port #(my_transaction) port; //获取数据的端口,#中表示这个端口传递的数据类型是my_transaction

uvm_analysis_port #(my_transaction) ap; // 发送数据的端口

extern function new(string name, uvm_component parent);

extern function void build_phase(uvm_phase phase);

extern virtual task main_phase(uvm_phase phase);

`uvm_component_utils(my_model)

endclass

function my_model::new(string name, uvm_component parent);

super.new(name, parent);

endfunction

function void my_model::build_phase(uvm_phase phase);

super.build_phase(phase);

port = new("port", this);

ap = new("ap", this);

endfunction

task my_model::main_phase(uvm_phase phase);

my_transaction tr;

my_transaction new_tr;

super.main_phase(phase);

while(1) begin // 循环执行

port.get(tr);

new_tr = new("new_tr");

new_tr.copy(tr); // 这里是因为DUT 本身就是直接传递数据,所以计算出来的tr其实就是复制一份。

`uvm_info("my_model", "get one transaction, copy and print it:", UVM_LOW)

// new_tr.print(); // 打印信息

ap.write(new_tr);

end

endtask

`endif我们知道,reference model具有一个输入端口和一个输出端口,并且端口的数据类型都是transaction,那么就有两个port,分别是uvm_blocking_get_port和uvm_analysis_port。前者是阻塞式的,会等待一个transaction传进来才会执行其他的动作,而后者则是直接把transaction传出去就不管了,然后继续执行其他的动作。也很好理解,没有trasaction进来那么就没办法去计算对应的输出,只要输出计算完了就可以直接把数据发送出去等待下一个trasaction进来。

这里对port的操作有两种,各种是get,一种是write,分别对应取数据和写数据。

2. scoreboard

Scoreboard 用于 结果验证 和 比较预期值与实际值,以确保设计(DUT,Device Under Test)的行为符合预期。简单来说,Scoreboard 就是一个用于验证 DUT 输出正确性 的 检查和记录器。

`ifndef MY_SCOREBOARD__SV

`define MY_SCOREBOARD__SV

class my_scoreboard extends uvm_scoreboard;

my_transaction expect_queue[$];

uvm_blocking_get_port #(my_transaction) exp_port;

uvm_blocking_get_port #(my_transaction) act_port;

`uvm_component_utils(my_scoreboard)

extern function new(string name, uvm_component parent = null);

extern virtual function void build_phase(uvm_phase phase);

extern virtual task main_phase(uvm_phase phase);

endclass

function my_scoreboard::new(string name, uvm_component parent = null);

super.new(name, parent);

endfunction

function void my_scoreboard::build_phase(uvm_phase phase);

super.build_phase(phase);

exp_port = new("exp_port", this);

act_port = new("act_port", this);

endfunction

task my_scoreboard::main_phase(uvm_phase phase);

my_transaction get_expect, get_actual, tmp_tran;

bit result;

super.main_phase(phase);

fork

while (1) begin

exp_port.get(get_expect);

expect_queue.push_back(get_expect);

end

while (1) begin

act_port.get(get_actual);

if(expect_queue.size() > 0) begin

tmp_tran = expect_queue.pop_front();

result = get_actual.compare(tmp_tran);

if(result) begin

`uvm_info("my_scoreboard", "Compare SUCCESSFULLY", UVM_LOW);

end

else begin

`uvm_error("my_scoreboard", "Compare FAILED");

$display("the expect pkt is");

tmp_tran.print();

$display("the actual pkt is");

get_actual.print();

end

end

else begin

`uvm_error("my_scoreboard", "Received from DUT, while Expect Queue is empty");

$display("the unexpected pkt is");

get_actual.print();

end

end

join

endtask

`endif类似的,scoreboard也需要有两个端口,一个来源与reference model,一个来源于DUT 输出端口的monitor,分别对应exp_port,和act_port。

socreboard执行两个任务,一个是不停的接收reference model的数据,另一个是不停接收monitor的数据,对照代码我们可以看到一些不同,即第二个while循环认定act_port能够get到数据时,expect_queue一定不会是空的。这个很好理解,DUT 和reference model 都是同时得到driver处的数据,但是DUT处理是需要依赖clock的,而reference model 是没有时钟的,立刻计算出正确数据。

3. 修改transaction的代码

在上两个模块中,我们直接使用了print、compare等函数,这些我们并没有定义,为什么能够直接使用呢?这是因为我们对transaction进行了注册,之前的注册方式`uvm_object_utils 并不能告诉平台,print的时候要输出哪些数据,所以我们还需要进行修改。

`ifndef MY_TRANSACTION__SV

`define MY_TRANSACTION__SV

class my_transaction extends uvm_sequence_item;

rand bit[47:0] dmac;

rand bit[47:0] smac;

rand bit[15:0] ether_type;

rand byte pload[];

rand bit[31:0] crc;

constraint pload_cons{

pload.size >= 46;

pload.size <= 1500;

}

function bit[31:0] calc_crc();

return 32'h0;

endfunction

function void post_randomize();

crc = calc_crc;

endfunction

`uvm_object_utils_begin(my_transaction) \\ 注册以下几个成员变量

`uvm_field_int(dmac, UVM_ALL_ON)

`uvm_field_int(smac, UVM_ALL_ON)

`uvm_field_int(ether_type, UVM_ALL_ON)

`uvm_field_array_int(pload, UVM_ALL_ON)

`uvm_field_int(crc, UVM_ALL_ON)

`uvm_object_utils_end

function new(string name = "my_transaction");

super.new();

endfunction

endclass

`endif4. 在monitor中添加端口

我们在RM 和SB 中添加了端口,那么还需要对应着添加monitor中的发送端口,类似的,我们可以得到;

`ifndef MY_MONITOR__SV

`define MY_MONITOR__SV

class my_monitor extends uvm_monitor;

virtual my_if vif;

uvm_analysis_port #(my_transaction) ap;

`uvm_component_utils(my_monitor)

function new(string name = "my_monitor", uvm_component parent = null);

super.new(name, parent);

endfunction

virtual function void build_phase(uvm_phase phase);

super.build_phase(phase);

if(!uvm_config_db#(virtual my_if)::get(this, "", "vif", vif))

`uvm_fatal("my_monitor", "virtual interface must be set for vif!!!")

ap = new("ap", this);

endfunction

extern task main_phase(uvm_phase phase);

extern task collect_one_pkt(my_transaction tr);

endclass

task my_monitor::main_phase(uvm_phase phase);

my_transaction tr;

while(1) begin

tr = new("tr");

collect_one_pkt(tr);

ap.write(tr);

end

endtask

task my_monitor::collect_one_pkt(my_transaction tr); // 这里的函数实现修改了,但是无需在意,只是利用了transaction 注册后的一些特性

byte unsigned data_q[$];

byte unsigned data_array[];

logic [7:0] data;

logic valid = 0;

int data_size;

while(1) begin

@(posedge vif.clk);

if(vif.valid) break;

end

`uvm_info("my_monitor", "begin to collect one pkt", UVM_LOW);

while(vif.valid) begin

data_q.push_back(vif.data);

@(posedge vif.clk);

end

data_size = data_q.size();

data_array = new[data_size];

for ( int i = 0; i < data_size; i++ ) begin

data_array[i] = data_q[i];

end

tr.pload = new[data_size - 18]; //da sa, e_type, crc

data_size = tr.unpack_bytes(data_array) / 8;

`uvm_info("my_monitor", "end collect one pkt", UVM_LOW);

endtask

`endif`ifndef MY_AGENT__SV

`define MY_AGENT__SV

class my_agent extends uvm_agent ;

my_driver drv;

my_monitor mon;

uvm_analysis_port #(my_transaction) ap;

function new(string name, uvm_component parent);

super.new(name, parent);

endfunction

extern virtual function void build_phase(uvm_phase phase);

extern virtual function void connect_phase(uvm_phase phase);

`uvm_component_utils(my_agent)

endclass

function void my_agent::build_phase(uvm_phase phase);

super.build_phase(phase);

if (is_active == UVM_ACTIVE) begin

drv = my_driver::type_id::create("drv", this);

end

mon = my_monitor::type_id::create("mon", this);

endfunction

function void my_agent::connect_phase(uvm_phase phase);

super.connect_phase(phase);

ap = mon.ap;

endfunction

`endif除了在monitor中定义,我们还需要在agent里面定义,这是然后将agent中的ap的指针指向monitor的port,这样做的目的就是避免层次结构混乱,对monitor的操作都可以在agent中进行。

5. 在env中连接端口

`ifndef MY_ENV__SV

`define MY_ENV__SV

class my_env extends uvm_env;

my_agent i_agt;

my_agent o_agt;

my_model mdl;

my_scoreboard scb;

uvm_tlm_analysis_fifo #(my_transaction) agt_scb_fifo; // #表示fifo中存储单元是my_transaction

uvm_tlm_analysis_fifo #(my_transaction) agt_mdl_fifo;

uvm_tlm_analysis_fifo #(my_transaction) mdl_scb_fifo;

function new(string name = "my_env", uvm_component parent);

super.new(name, parent);

endfunction

virtual function void build_phase(uvm_phase phase);

super.build_phase(phase);

i_agt = my_agent::type_id::create("i_agt", this);

o_agt = my_agent::type_id::create("o_agt", this);

i_agt.is_active = UVM_ACTIVE;

o_agt.is_active = UVM_PASSIVE;

mdl = my_model::type_id::create("mdl", this);

scb = my_scoreboard::type_id::create("scb", this);

agt_scb_fifo = new("agt_scb_fifo", this);

agt_mdl_fifo = new("agt_mdl_fifo", this);

mdl_scb_fifo = new("mdl_scb_fifo", this);

endfunction

extern virtual function void connect_phase(uvm_phase phase);

`uvm_component_utils(my_env)

endclass

function void my_env::connect_phase(uvm_phase phase);

super.connect_phase(phase);

i_agt.ap.connect(agt_mdl_fifo.analysis_export);

mdl.port.connect(agt_mdl_fifo.blocking_get_export);

mdl.ap.connect(mdl_scb_fifo.analysis_export);

scb.exp_port.connect(mdl_scb_fifo.blocking_get_export);

o_agt.ap.connect(agt_scb_fifo.analysis_export);

scb.act_port.connect(agt_scb_fifo.blocking_get_export);

endfunction

`endif这里我们定义了三个fifo,fifo的两个端口也需要分别与我们在组件中定义的端口相连,定义的是阻塞就连阻塞,定义的是非阻塞就连非阻塞。

至此,我们可以运行程序,下面补上driver和tb_top的内容:

`ifndef MY_DRIVER__SV

`define MY_DRIVER__SV

class my_driver extends uvm_driver;

virtual my_if vif;

`uvm_component_utils(my_driver)

function new(string name = "my_driver", uvm_component parent = null);

super.new(name, parent);

endfunction

virtual function void build_phase(uvm_phase phase);

super.build_phase(phase);

if(!uvm_config_db#(virtual my_if)::get(this, "", "vif", vif))

`uvm_fatal("my_driver", "virtual interface must be set for vif!!!")

endfunction

extern task main_phase(uvm_phase phase);

extern task drive_one_pkt(my_transaction tr);

endclass

task my_driver::main_phase(uvm_phase phase);

my_transaction tr;

phase.raise_objection(this);

vif.data <= 8'b0;

vif.valid <= 1'b0;

while(!vif.rst_n)

@(posedge vif.clk);

for(int i = 0; i < 2; i++) begin

tr = new("tr");

assert(tr.randomize() with {pload.size == 200;});

drive_one_pkt(tr);

end

repeat(5) @(posedge vif.clk);

phase.drop_objection(this);

endtask

task my_driver::drive_one_pkt(my_transaction tr);

byte unsigned data_q[];

int data_size;

data_size = tr.pack_bytes(data_q) / 8;

`uvm_info("my_driver", "begin to drive one pkt", UVM_LOW);

repeat(3) @(posedge vif.clk);

for ( int i = 0; i < data_size; i++ ) begin

@(posedge vif.clk);

vif.valid <= 1'b1;

vif.data <= data_q[i];

end

@(posedge vif.clk);

vif.valid <= 1'b0;

`uvm_info("my_driver", "end drive one pkt", UVM_LOW);

endtask

`endif`timescale 1ns/1ps

`include "uvm_macros.svh"

import uvm_pkg::*;

`include "my_if.sv"

`include "my_transaction.sv"

`include "my_driver.sv"

`include "my_monitor.sv"

`include "my_agent.sv"

`include "my_model.sv"

`include "my_scoreboard.sv"

`include "my_env.sv"

module top_tb;

reg clk;

reg rst_n;

reg[7:0] rxd;

reg rx_dv;

wire[7:0] txd;

wire tx_en;

my_if input_if(clk, rst_n);

my_if output_if(clk, rst_n);

dut my_dut(.clk(clk),

.rst_n(rst_n),

.rxd(input_if.data),

.rx_dv(input_if.valid),

.txd(output_if.data),

.tx_en(output_if.valid));

initial begin

clk = 0;

forever begin

#100 clk = ~clk;

end

end

initial begin

rst_n = 1'b0;

#1000;

rst_n = 1'b1;

end

initial begin

run_test("my_env");

end

initial begin

uvm_config_db#(virtual my_if)::set(null, "uvm_test_top.i_agt.drv", "vif", input_if);

uvm_config_db#(virtual my_if)::set(null, "uvm_test_top.i_agt.mon", "vif", input_if);

uvm_config_db#(virtual my_if)::set(null, "uvm_test_top.o_agt.mon", "vif", output_if);

end

endmodule更新以下filelist.f:

+incdir+$UVM_HOME/src

$UVM_HOME/src/uvm_pkg.sv

../dut/dut.sv

top_tb.sv

my_driver.sv

my_if.sv

my_transaction.sv

my_monitor.sv

my_agent.sv

my_env.sv

my_scoreboard.sv

my_model.sv文件树如下:

├── 2.3.7

│ ├── filelist.f

│ ├── Makefile

│ ├── my_agent.sv

│ ├── my_driver.sv

│ ├── my_env.sv

│ ├── my_if.sv

│ ├── my_model.sv

│ ├── my_monitor.sv

│ ├── my_scoreboard.sv

│ ├── my_transaction.sv

│ └── top_tb.sv

└── dut

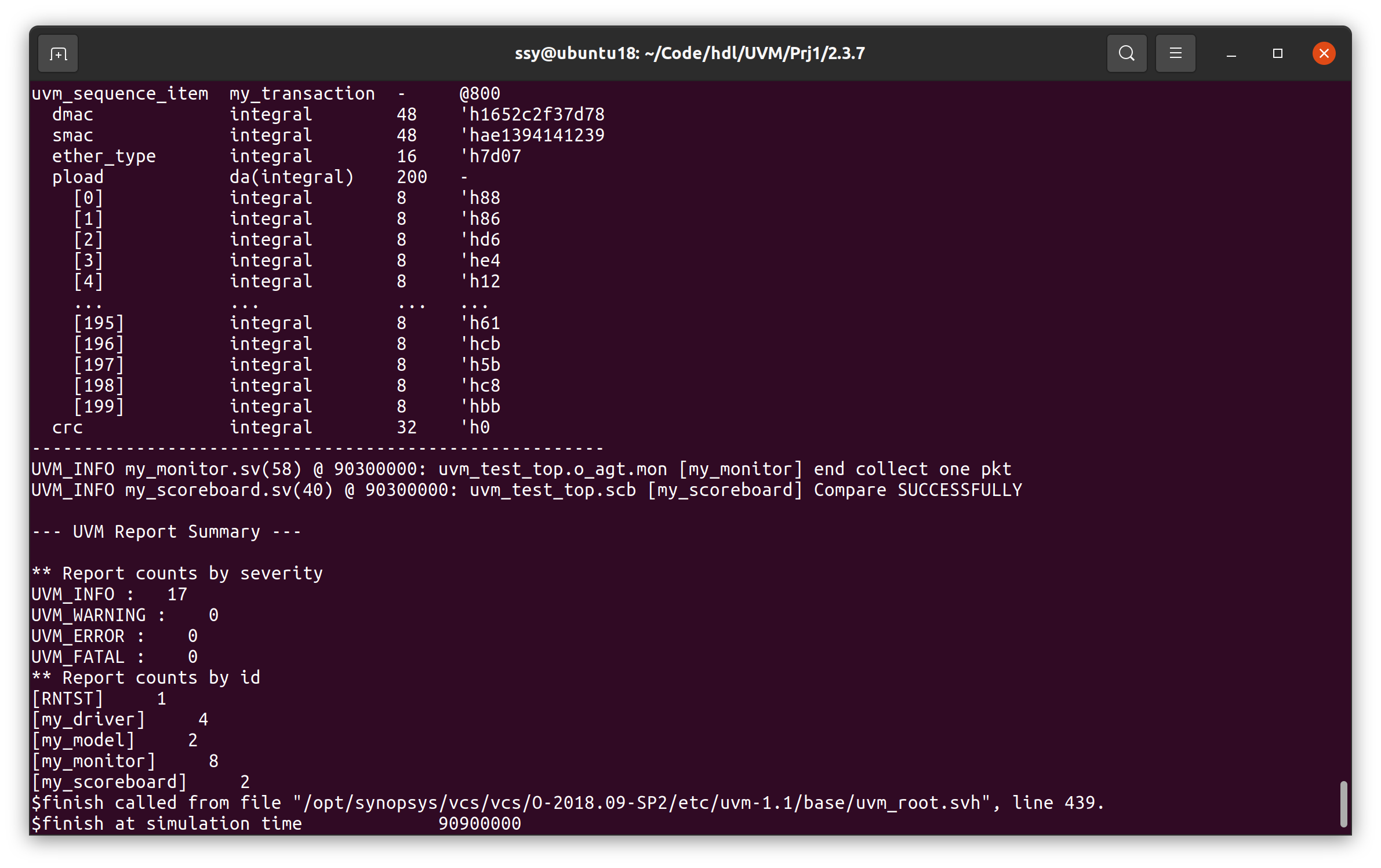

└── dut.sv执行得到:

《UVM实战》运行第一个验证平台 STEP5

https://blog.songshiyu.cn/archives/uvmshi-zhan-yun-xing-di-yi-ge-yan-zheng-ping-tai-step5

评论