本文最后更新于2025-01-01,距今已有 503 天,若文章内容或图片链接失效,请留言反馈。

使用环境是Ubuntu20.04+VCS2018+Verdi2018,笔记本是R7-8845HS+32G。 目前尝试过vcs的安装环境18.04和20.04都可以,但是24.04不行,报错无法解决。安装教程之后会录制视频和文图。

1. DUT 文件

本次仿真用了一个简单的RAM,仿真测试RAM 的读写:

module MRAM #(

// define parameter

parameter RAM_ADDR_WDITH = 4,

parameter RAM_DATA_WDITH = 9,

parameter U_DLY = 1

)

(

input a_clk,

input [RAM_DATA_WDITH-1:0] a_wr_data,

input a_wr_en,

input [RAM_ADDR_WDITH-1:0] a_wr_addr,

input b_clk,

output reg [RAM_DATA_WDITH-1:0] b_rd_data,

input b_rd_en,

input [RAM_ADDR_WDITH-1:0] b_rd_addr

);

localparam RAM_DEPTH = 1<< RAM_ADDR_WDITH;

// define wire and reg

reg [RAM_DATA_WDITH-1:0] mem [RAM_DEPTH-1:0];

always@(posedge a_clk)begin

if (a_wr_en) begin

mem[a_wr_addr] <= #U_DLY a_wr_data;

end

else begin

mem <= #U_DLY mem;

end

end

always @(posedge b_clk) begin

if(b_rd_en)begin

b_rd_data <= #U_DLY mem[b_rd_addr];

end

else

b_rd_data <= #U_DLY b_rd_data;

end

endmodule2. TestBench

`timescale 1ns/100ps

module tb_top ();

parameter ADDR_WIDTH = 4;

parameter DATA_WIDTH = 9 ;

parameter U_DLY = 1;

reg clk;

reg wr_en;

reg rd_en;

reg [ADDR_WIDTH-1:0] wr_addr ;

reg [ADDR_WIDTH-1:0] rd_addr ;

reg [DATA_WIDTH-1:0] wdata ;

wire [DATA_WIDTH-1:0] rdata ;

MRAM ram(

.a_clk(clk),

.b_clk(clk),

.a_wr_data(wdata),

.a_wr_en(wr_en),

.a_wr_addr(wr_addr),

.b_rd_data(rdata),

.b_rd_en(rd_en),

.b_rd_addr(rd_addr)

);

initial begin

wr_addr =0;

rd_addr =0;

wdata =0;

wr_en =0;

rd_en = 0;

clk = 0;

#50

wr_en =1;

# 500

wr_en =0;

#50

rd_en =1;

#500

$finish;

end

always @(posedge clk) begin

wr_addr <= #U_DLY wr_addr +1;

rd_addr <= #U_DLY wr_addr-1;

wdata <= #U_DLY wr_addr+1;

end

always #5 clk = ~clk;

initial begin

$fsdbDumpfile("tb_top.fsdb");

$fsdbDumpvars(0,tb_top);

$fsdbDumpMDA();

end

endmodule3. filelist.f

./tb_top.sv

../src/MRAM.v4. Makefile

vcs :

vcs \

-f filelist.f \

-LDFLAGS -Wl,--no-as-needed \

-fsdb -full64 -R +vc +v2k -sverilog -debug_all \

| tee vcs.log

verdi :

verdi -sv -f filelist.f -ssf tb_top.fsdb &

clean :

rm -rf *.log simv *.daidir csrc *.key DVEfiles *.vpd *.conf *.rc *.fsdb verdiLog

5. 文件路径

.

├── sim_ut

│ ├── filelist.f

│ ├── Makefile

│ └── tb_top.sv

└── src

└── MRAM.v在sim_ut 路径下,执行 make vcs:

(C) 1996 - 2019 by Synopsys, Inc.

*Verdi* : Create FSDB file 'tb_top.fsdb'

*Verdi* : Begin traversing the scope (tb_top), layer (0).

*Verdi* : End of traversing.

*Verdi* : Begin traversing the MDAs, layer (0).

*Verdi* : Enable +mda and +packedmda dumping.

*Verdi* : End of traversing the MDAs.

$finish called from file "./tb_top.sv", line 43.

$finish at simulation time 51500

V C S S i m u l a t i o n R e p o r t

Time: 5150000 ps

CPU Time: 0.160 seconds; Data structure size: 0.0Mb

Sat Dec 21 18:13:08 2024

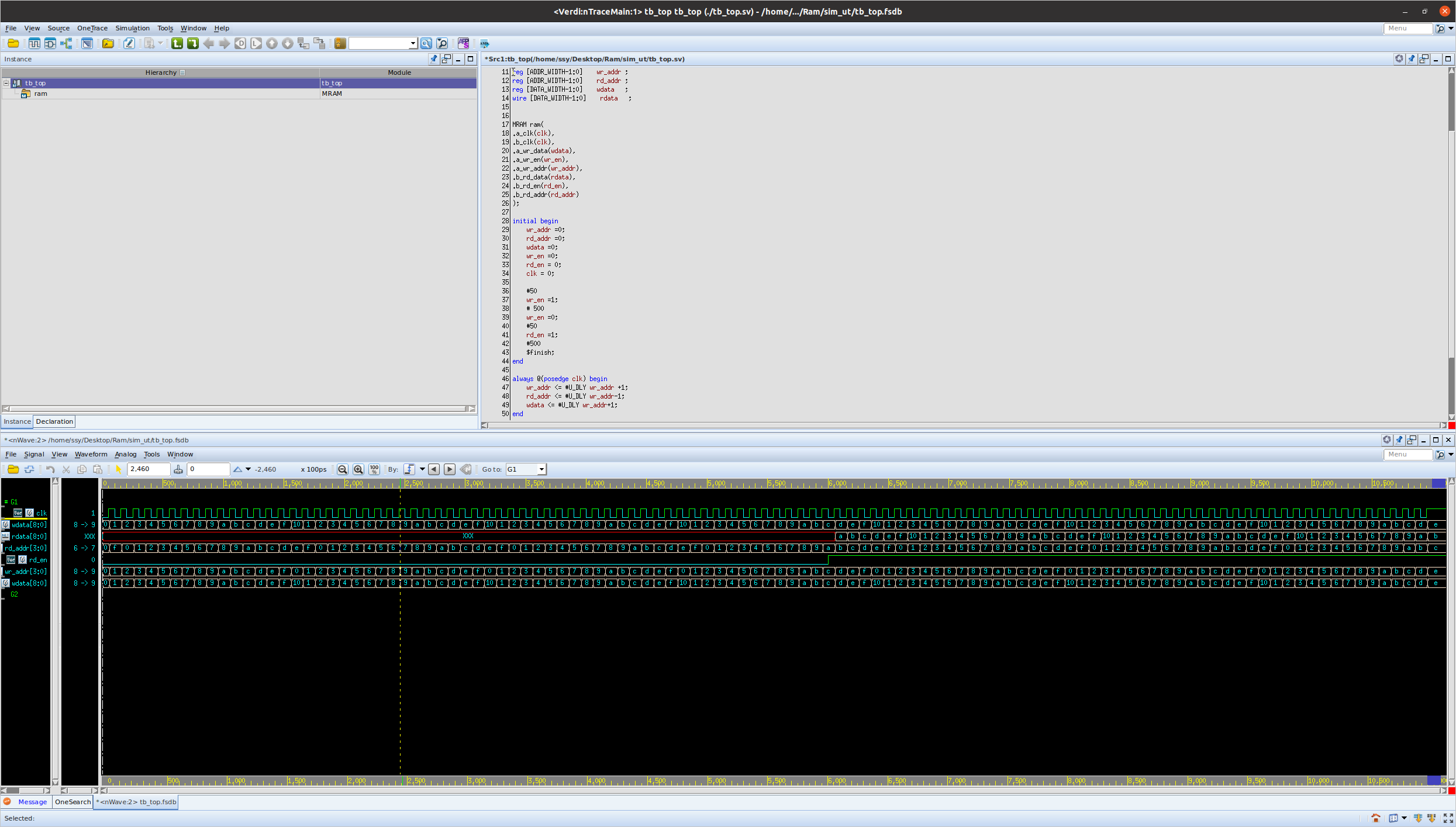

CPU time: .147 seconds to compile + .180 seconds to elab + .180 seconds to link + .197 seconds in simulation执行 make verdi :

VCS+Verdi 仿真实例+Makefile脚本

https://blog.songshiyu.cn/archives/vcs-verdi-fang-zhen-shi-li-makefilejiao-ben

评论